# Explications supplémentaires Exercice Synthèse de fréquence – diviseur à double modulo

### Quelques notions sur les systèmes télécom.

- Bande radio CB (bande citoyenne, citizens' band) est utilisée pour tous types de communications radio privées et non commerciales dans la bande des 27 MHz.

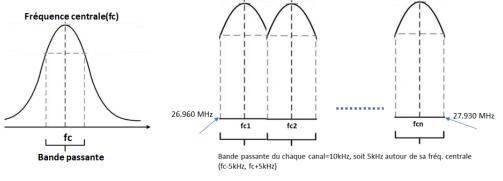

- Fréquence centrale des canaux et bande passante d'un canal

Fréq. centrale et bande passante d'un seul canal Les fréq. centrales à synthétiser: 26.965 MHz à 27.925 MHz II est important de considérer que chaque canal possède une bande passante autour de sa fréquence centrale, et cette bande passante doit être incluse dans la plage de fréquences à la sortie du VCO

# <u>Dimensionnement des compteurs N et A (càd choisir les valeurs max et min de manière à couvrir la plage demandée</u>

Pour avoir une plage de valeurs de division totales en séquence, le compteur A est programmé de zéro à P-1 pour une valeur particulière N dans le compteur N. N est ensuite incrémenté de 1 et le compteur A est séquencé de zéro à P-1 à nouveau.

## Certaines contraintes s'appliquent :

- (1) N > A

- (2)  $0 \le A \le P-1$

**Question**: Quel risque si cette condition n'est pas vérifiée, par exemple si  $0 \le A \le 5$  et P=8? Prenez un cas particulier et justifier avec les équations et valeurs numériques.

**Réponse** : Si cette relation n'est pas respectée, il y a le risque de ne pas pouvoir couvrir toute la gamme des valeurs pour la fréquence synthétisée fOSC .

- (3) La valeur maximale de A et surtout celle de N qui est plus grande doivent pouvoir être contenus dans les compteurs (s'assurer que les compteurs ont le nombre de bits nécessaires)

- (4) On doit vérifier que fosc/P est inférieure à la fréq maximale admise à l'entrée des compteurs A et N. Il convient de noter que les compteurs programmables nécessitent un temps de recharge à chaque 'carry out', ce qui impose des limitations sur leur vitesse (fréquence de l'horloge d'entrée)

On remarque qu'avec la contrainte A≤P-1 on ne peut pas couvrir toute la bande passante de la fréquence centrale maximale (fc=27'925 +5 KHz), mais cela n'est pas problématique, car il manque seulement 3kHz. De plus, la fréquence centrale peut de toute manière être synthétisée.

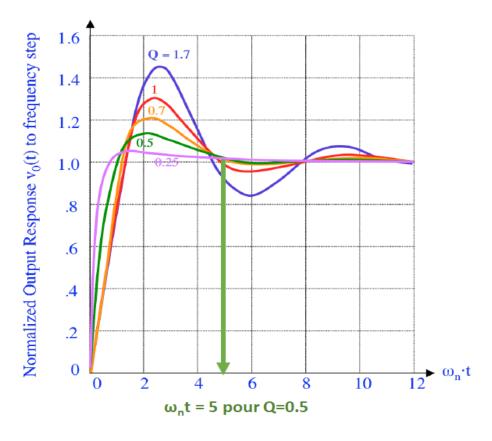

# Réponse en tension à un saut de fréquence pour filtre intégrateur de degré 1, Q=0.5 (voir polycopie, graph page 20, chapitre PLL-comportement dynamique)

#### Dimensionnement du filtre de degré 1 intégrateur avec un zéro

La valeur de la résistance fictive R1 utilisée dans le calcul de la fonction de transfert est **fixée par le fabricant à R1=VDD/2I**, où I est le courant généré par les sources de courant de la pompe de charge. Les valeurs de VDD et I sont généralement spécifiées dans les exercices (ou sur le schéma du circuit), donc vous devez déduire la valeur de R1 comme indiqué.

#### Détecteur phase-fréquence avec pompe de charge : l'avantage d'un filtre passe-bas de 2ème dégrée

Le détecteur de phase produit des impulsions de largeur variable (proportionnelle à l'écart de phase  $\Phi = \Phi_{\text{IN}} - \Phi_{\text{OUT}}$ ) qui activent les interrupteurs pour charger ou décharger le condensateur C (suivant que  $\Phi > 0$  or  $\Phi < 0$ ). La tension de commande Vo (sortie du filtre qui contrôle le VCO) oscillera avant de se stabiliser à sa valeur en régime permanent. Cela se produit parce qu'on ne peut pas changer instantanément la tension à travers un condensateur, donc la chute de tension initiale se produit à travers R2, ce qui charge ensuite la tension sur C de manière exponentielle. Cette variation brusque de la tension de commande module en fréquence le VCO à la fréquence d'entrée  $f_{\text{IN}}$ , créant ainsi des pics dans le spectre de la fosc (qu'on appelle aussi 'spurs', voir slide 26 du cours sur la synthèse de fréquence). Ainsi, il faut corriger cela en ajoutant un second condensateur, C2, dont la fonction est de filtrer les composants bruit haute fréquence du réseau série R2C. L'amplitude des pics sera ainsi réduite et la tension Vo sera d'avantagé lissée avant de contrôler le VCO.

Cependant, C2 ajoute un troisième pôle de fréquence finie qui réduira la stabilité de la PLL. Avec ce filtre d'ordre 2 (donc une PLL d'ordre 3), les outils pratiques que nous avons utilisés pour étudier le comportement dynamique de la PLL du second ordre ne sont plus précis. Une solution pratique consiste à vérifie la stabilité de la PLL en utilisant les diagrammes de Bode et la marge de phase.

PLL est un circuit avec une boucle de réaction négative. La définition et le calcul de la marge de phase sont similaires à ceux décrits pour l'étude de la stabilité de l'amplificateur opérationnel avec réaction négative (voir polycopie, chapitre "Réaction négative", page 34).

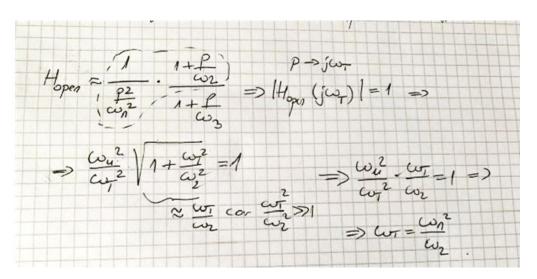

• Pour calculer la marge de phase if faut déterminer  $\omega_T$ . La technique consiste à considérer premièrement la fonction de transfert avec le pole en origine (intégrateur) et le zéro, et après choisir l'emplacement du  $2^{\text{ème}}$  pole ( $\omega_3$ ) en fonction de la marge de phase souhaitée.

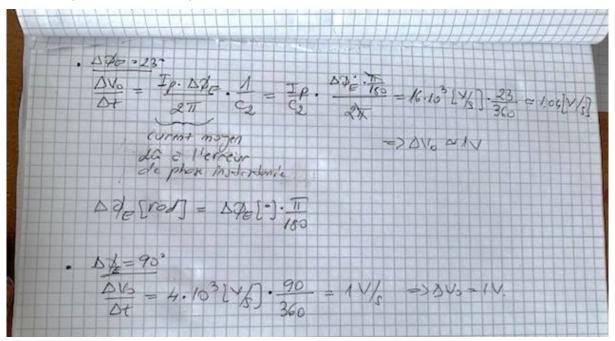

•  $\Delta V_0$  pour une erreur de phase transitoire,  $\Delta \varphi_E$ :

### Remarques:

- Ces filtres, simples à réaliser car composés uniquement de composants passifs, sont préférables aux filtres réalisés avec des amplificateurs opérationnels. En effet, ils offrent des performances équivalentes tout en évitant l'utilisation de composants actifs, ce qui simplifie la conception du circuit PLL.

- A noter que dans l'application synthèse de fréquence, f<sub>IN</sub> fixe et f<sub>OUT</sub> est variable. La PLL a pour rôle de capturer et verrouiller f<sub>OUT</sub> sur f<sub>IN</sub>. La capture est nécessaire chaque fois que le facteur de division programmable est modifié (de l'extérieur) pour sélectionner une autre fréquence synthétisée f<sub>OSC</sub> à la sortie.